Nächste Seite: Pause, nachher einen Termin Aufwärts: 2024-11-03 Vorherige Seite: Das Interrupt benutzen um

ich mache jetzt eine neue VHDL Übung, die werde ich für den MIPS32 noch brauchen, ich schreibe jeden Tag ein RS-Latch. Problem, wie ein RS-Latch, funktioniert weiss ich - aber man muss es in VHDL realisieren können. dazu muss es von alleine gehen. Damit fange ich jetzt an, ich habe es ein paar Mal getan.

Es gibt dabei ein paar Dinge, die immer klar sind und ein paar Dinge, die immer unklar sind - zunächst, wenn ich in VHDL Code schreibe, es gibt genau zwei Möglichkeiten

Und ich sage gleich, wenn ich den MIPS32 später mache, dann werde ich beide anwenden. Ich werde zwei verschiedene Formen von Codes schreiben

1.) Die eine ist eine fast reine Schaltungsbeschreibung - sie setzt die Gatter so zusammen, wie man es in der Realität tun würde 2.) die andere ist eine, die alle Vorzüge von VHDL verwendet

Nichts desto trotz, ich finde erstere gut. Einen MIPS32 realisieren ist realativ einfach

Ein RS-Latch auch. Allerdings hakt es hier in VHDL - man weiss ja ein RS-Latch kann zustände annehmen, die es nicht annehmen darf. Das verbietet VHDL

Ich denke ein einfacher MIPS32, lässt sich sehr schnell zusammensetzen, wenn die Komponenten da sind

Mein Ziel ist es nicht nur einen MIPS32, zu realisieren, um zu frieden zu sein, ich habe es geschafft. Genau wie ich bei TTL Gattern Übungen mache, damit es tut und ich nicht irgendein gigantisches Endprodukt habe, was ich letzten Endes selber nicht mehr verstehe, will ich nebenbei VHDL lernen

Das heisst, es geht darum zu lernen, ein RS-Latch jeder Zeit schreiben zu können

Wie immer schreibe ich jetzt zunächst den Code, den ich ëinfach soßchreiben kann, ich ergänze ihn dann.

-- wuerde es funktionieren, w"urde es vereinfacht so aussehen

library ieee;

use ieee.std_logic_1164.all;

entity rs_latch_20241104 is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rs_latch_20241104 is

begin

q <= (r nor qs);

qs <= (s nor q);

end;

Weiter:

library ieee;

use ieee.std_logic_1164.all;

entity rs_latch_20241104 is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rs_latch_20241104 is

begin

q <= (r nor qs);

qs <= (s nor q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity rs_latch_20241104_testbench is

port (

q: inout std_logic

);

end;

architecture behaviour of rs_latch_20241104_testbench is

component rs_latch_20241104

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal r, s: std_logic;

begin

rs: rs_latch_20241104 PORT MAP (r=>r, s=>s, q=>q);

end;

Und noch weiter:

library ieee;

use ieee.std_logic_1164.all;

entity rs_latch_20241104 is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rs_latch_20241104 is

begin

q <= (r nor qs);

qs <= (s nor q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity rs_latch_20241104_testbench is

port (

q: inout std_logic

);

end;

architecture behaviour of rs_latch_20241104_testbench is

component rs_latch_20241104

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal r, s: std_logic;

begin

rs: rs_latch_20241104 PORT MAP (r=>r, s=>s, q=>q);

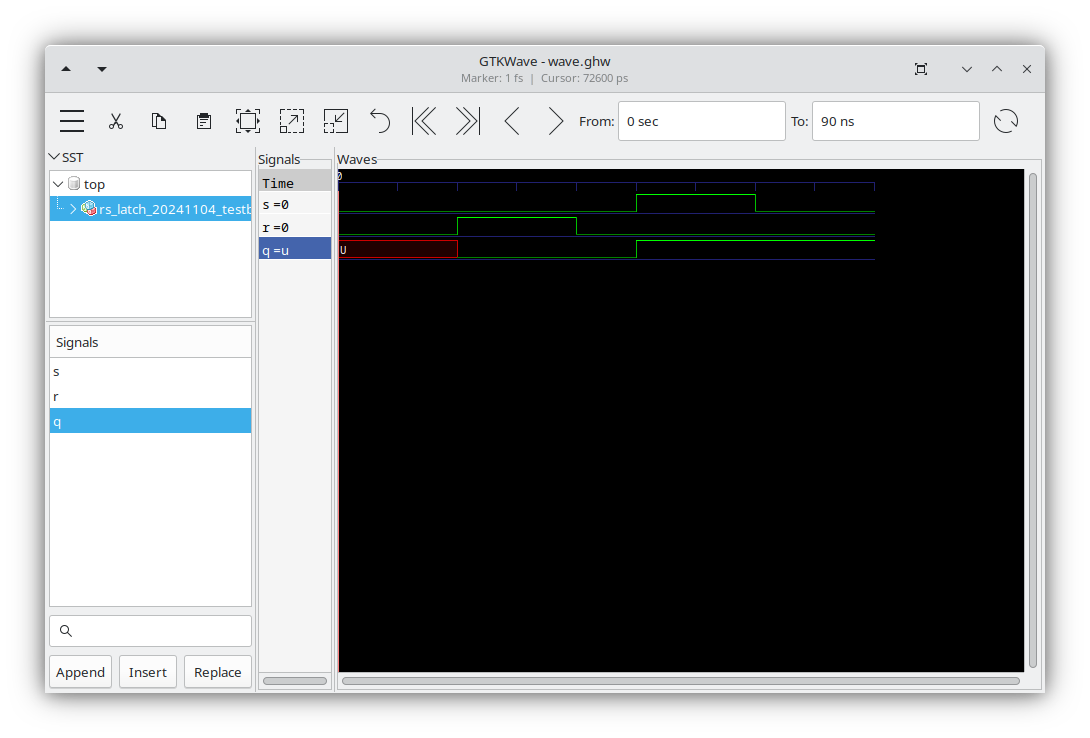

r <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns;

s <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns;

end;

Es ist etwas seltsames passiert, seltsamer weise, ich weiss nicht, woher die angeblichen Fehler stammen, die dann entstehen, wahrscheinlich sind sie eine Erfindung durch einen selber, die bei ihrer ersten Erfindung gegen sich selbst, immer mehr fehler erzeugen, so, dass das Problem am Ende wird, wie es nicht ist, denn

david@work:~$ ghdl -a rslatch20241104_002.vhdl david@work:~$ ghdl -r rs_latch_20241104_testbench --wave=wave.ghw david@work:~$ gtkwave wave.ghwDas Programm liess sich problemlos übersetzen. Frage: Lässt sich das Programm auch darstellen, mit gtkwave?

Antwort: Ja

ich bin aber noch vorsichtig, ob es seinen Zustand wirklich behält und wir haben noch ein Problem

Das Latch ist am Anfang in einem undefinierbaren Zustand. Es lässt sich zwar so übersetzen - aber: wenn wir das zu Registern nachher zusammenbauen, gibt es später fehler und der Prozessor tut erst mal gar nicht. Weil er in diesem Zustand ist

Wir müssten, wenn wir nicht die Prozesse mit conditions usw. von VHDL nutzen wollen, wenigstens ein Bit in alle Latches schlussendlich einsetzen,mit der alle geresettet werden

library ieee;

use ieee.std_logic_1164.all;

entity rs_latch_20241104 is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rs_latch_20241104 is

begin

q <= (r nor qs);

qs <= (s nor q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity rs_latch_20241104_testbench is

port (

q: inout std_logic

);

end;

architecture behaviour of rs_latch_20241104_testbench is

component rs_latch_20241104

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal r, s: std_logic;

begin

rs: rs_latch_20241104 PORT MAP (r=>r, s=>s, q=>q);

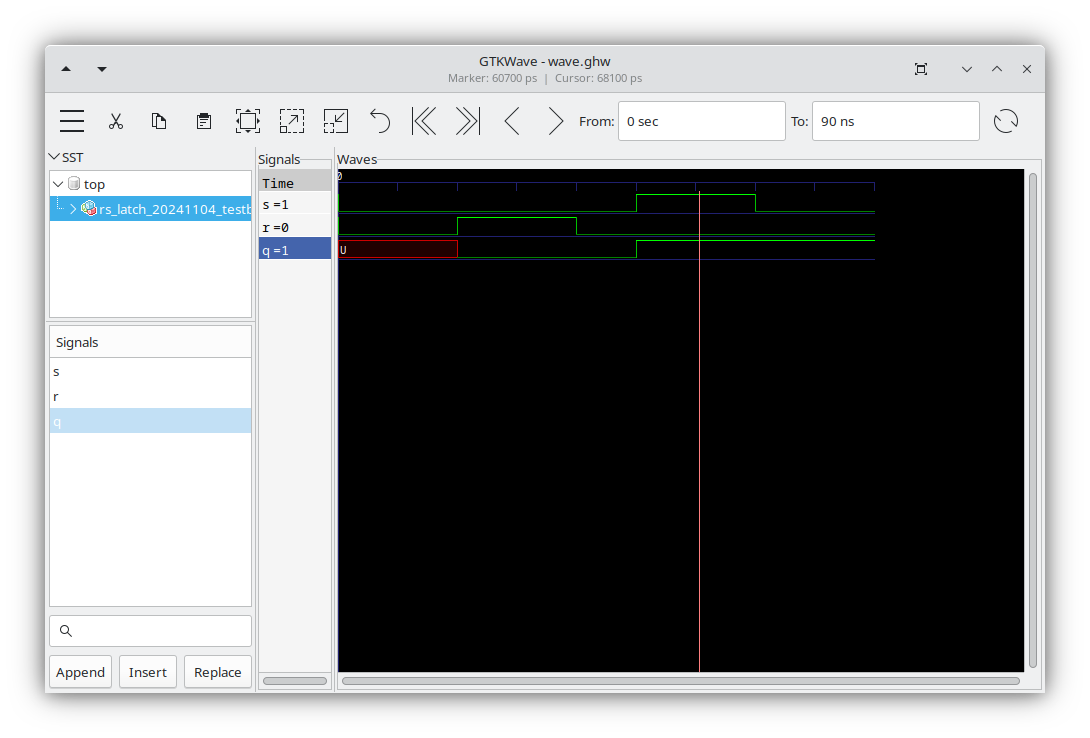

r <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns;

s <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns;

end;

Das Latch hat seinen Zustand behalten und funktioniert perfekt. Ich werde es zu den täglichen Übungen tun. Und ich werde nicht auf den MIPS32, hin arbeiten Wenn die übung oft genug geschehen ist, werde ich sie ergänzen, dieselbe Übung, aber daraus wird ein Taktgesteuertes RS-Latch, daraus ein D-Latch. Das findet unabhängig vom MIPS32, statt Der Fehler in der Zukunft wird jetzt noch vernachlässigt.