Nächste Seite: Komplexe Schaltwerk Übung Aufwärts: Übungen Vorherige Seite: state20241130.txt

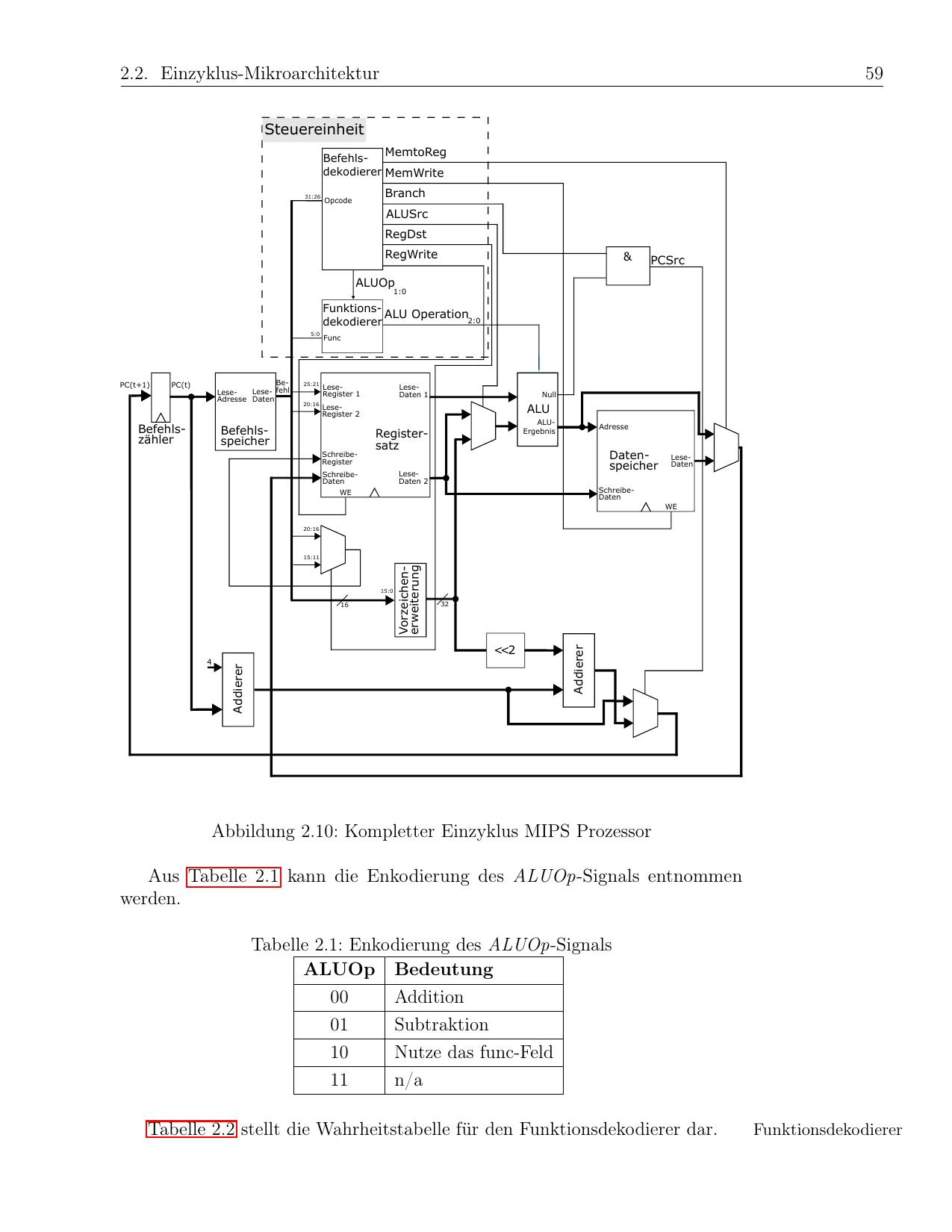

32 Bit Ripple Carry Chain Addierer

-- (C) David Vajda

-- 32 Bit Ripple Carry Chain Adder / Subtrahierer / Volladdierer

-- 2024-12-02

library ieee;

use ieee.std_logic_1164.all;

entity fulladder is

port (

a: in std_logic;

b: in std_logic;

c: out std_logic;

s: in std_logic;

t: out std_logic

);

end;

architecture behaviour of fulladder is

begin

c <= a xor b xor s;

t <= (a and b) or ((a or b) and s);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarrychainadder32 is

port (

a: in std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

c: out std_logic_vector (31 downto 0);

s: in std_logic;

t: out std_logic

);

end;

architecture behaviour of ripplecarrychainadder32 is

component fulladder

port (

a: in std_logic;

b: in std_logic;

c: out std_logic;

s: in std_logic;

t: out std_logic

);

end component;

signal x: std_logic_vector (32 downto 0);

begin

fa_loop: FOR i IN 31 DOWNTO 0 GENERATE

fa: fulladder PORT MAP (a=>a(i), b=>b(i), c=>c(i), s=>x(i), t=>x(i+1));

END GENERATE;

t <= x (32) ;

x (0) <= s;

--fa3: fulladder20241128 PORT MAP (a=>a3, b=>b3, c=>c3, s=>s3, t=>t);

--fa2: fulladder20241128 PORT MAP (a=>a2, b=>b2, c=>c2, s=>s2, t=>s3);

--fa1: fulladder20241128 PORT MAP (a=>a1, b=>b1, c=>c1, s=>s1, t=>s2);

--fa0: fulladder20241128 PORT MAP (a=>a0, b=>b0, c=>c0, s=>s, t=>s1);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarrychainadder32testbench is

port (

c: out std_logic_vector (31 downto 0);

t: out std_logic

);

end;

architecture behaviour of ripplecarrychainadder32testbench is

component ripplecarrychainadder32

port (

a: in std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

c: out std_logic_vector (31 downto 0);

s: in std_logic;

t: out std_logic

);

end component;

signal a: std_logic_vector (31 downto 0);

signal b: std_logic_vector (31 downto 0);

signal s: std_logic;

begin

rplcadd: ripplecarrychainadder32 PORT MAP (c=>c, b=>b, a=>a, s=>s, t=>t);

-- 19219 + 14823 = 34042

-- 0b100101100010011 + 0b11100111100111 = 0b1000010011111010

a <= ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 20 ns;

b <= ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','1','1', '1','0','0','1', '1','1','1','0', '0','1','1','1') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','1','1', '1','0','0','1', '1','1','1','0', '0','1','1','1') after 20 ns;

s <= '0';

end;

|

Subtrahierer:

-- (C) David Vajda

-- 32 Bit Ripple Carry Chain Adder / Subtrahierer / Volladdierer

-- 2024-12-02

library ieee;

use ieee.std_logic_1164.all;

entity fulladder is

port (

a: in std_logic;

b: in std_logic;

c: out std_logic;

s: in std_logic;

t: out std_logic

);

end;

architecture behaviour of fulladder is

begin

c <= a xor b xor s;

t <= (a and b) or ((a or b) and s);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarrychainadder32 is

port (

a: in std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

c: out std_logic_vector (31 downto 0);

s: in std_logic;

t: out std_logic

);

end;

architecture behaviour of ripplecarrychainadder32 is

component fulladder

port (

a: in std_logic;

b: in std_logic;

c: out std_logic;

s: in std_logic;

t: out std_logic

);

end component;

signal x: std_logic_vector (32 downto 0);

begin

fa_loop: FOR i IN 31 DOWNTO 0 GENERATE

fa: fulladder PORT MAP (a=>a(i), b=>b(i), c=>c(i), s=>x(i), t=>x(i+1));

END GENERATE;

t <= x (32) ;

x (0) <= s;

--fa3: fulladder20241128 PORT MAP (a=>a3, b=>b3, c=>c3, s=>s3, t=>t);

--fa2: fulladder20241128 PORT MAP (a=>a2, b=>b2, c=>c2, s=>s2, t=>s3);

--fa1: fulladder20241128 PORT MAP (a=>a1, b=>b1, c=>c1, s=>s1, t=>s2);

--fa0: fulladder20241128 PORT MAP (a=>a0, b=>b0, c=>c0, s=>s, t=>s1);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarrychainadder32testbench is

port (

c: out std_logic_vector (31 downto 0);

t: out std_logic

);

end;

architecture behaviour of ripplecarrychainadder32testbench is

component ripplecarrychainadder32

port (

a: in std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

c: out std_logic_vector (31 downto 0);

s: in std_logic;

t: out std_logic

);

end component;

signal a: std_logic_vector (31 downto 0);

signal b: std_logic_vector (31 downto 0);

signal s: std_logic;

begin

rplcadd: ripplecarrychainadder32 PORT MAP (c=>c, b=>b, a=>a, s=>s, t=>t);

-- 19219 + 14823 = 34042

-- 0b100101100010011 + 0b11100111100111 = 0b1000010011111010

a <= ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 20 ns;

b <= ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','1','1', '1','0','0','1', '1','1','1','0', '0','1','1','1') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','1','1', '1','0','0','1', '1','1','1','0', '0','1','1','1') after 20 ns;

s <= '0';

end;

library ieee;

use ieee.std_logic_1164.all;

entity com32 is

port (

x: in std_logic_vector (31 downto 0);

y: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of com32 is

begin

com_connect: FOR i IN 31 DOWNTO 0 GENERATE

y (i) <= not x (i);

END GENERATE;

end;

library ieee;

use ieee.std_logic_1164.all;

entity neg32 is

port (

b: out std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

t: out std_logic

);

end;

architecture behaviour of neg32 is

component com32

port (

x: in std_logic_vector (31 downto 0);

y: out std_logic_vector (31 downto 0)

);

end component;

component ripplecarrychainadder32

port (

a: in std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

c: out std_logic_vector (31 downto 0);

s: in std_logic;

t: out std_logic

);

end component;

signal c: std_logic_vector (31 downto 0);

signal d: std_logic_vector (31 downto 0);

signal s: std_logic;

begin

neg32_generate_1: FOR i IN 31 DOWNTO 0 GENERATE

d (i) <= '0';

END GENERATE;

s <= '1';

com: com32 PORT MAP (x=>a, y=>c);

add: ripplecarrychainadder32 PORT MAP (b=>d, a=>c, s=>s, t=>t, c=>b);

end;

library ieee;

use ieee.std_logic_1164.all;

entity sub32 is

port (

a: in std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

c: out std_logic_vector (31 downto 0);

t: out std_logic

);

end;

architecture behaviour of sub32 is

component ripplecarrychainadder32

port (

a: in std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

c: out std_logic_vector (31 downto 0);

s: in std_logic;

t: out std_logic

);

end component;

component neg32

port (

b: out std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

t: out std_logic

);

end component;

signal x: std_logic_vector (31 downto 0);

signal s: std_logic;

begin

neg: neg32 PORT MAP (a=>a, b=>x);

add: ripplecarrychainadder32 PORT MAP (b=>b, a=>x, c=>c, s=>s, t=>t);

s <= '0';

end;

library ieee;

use ieee.std_logic_1164.all;

entity sub32testbench is

port (

c: out std_logic_vector (31 downto 0);

t: out std_logic

);

end;

architecture behaviour of sub32testbench is

component sub32

port (

a: in std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

c: out std_logic_vector (31 downto 0);

t: out std_logic

);

end component;

signal a: std_logic_vector (31 downto 0);

signal b: std_logic_vector (31 downto 0);

signal s: std_logic;

begin

sub: sub32 PORT MAP (a=>a, b=>b, c=>c, t=>t);

a <= ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','1','1', '1','0','0','1', '1','1','1','0', '0','1','1','1') after 10 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','1','1', '1','0','0','1', '1','1','1','0', '0','1','1','1') after 20 ns;

b <= ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','1','1', '1','0','0','1', '1','1','1','0', '0','1','1','1') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 10 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 20 ns;

s <= '0' after 0 ns, '1' after 10 ns;

-- 19219 - 14823 =

end;

|

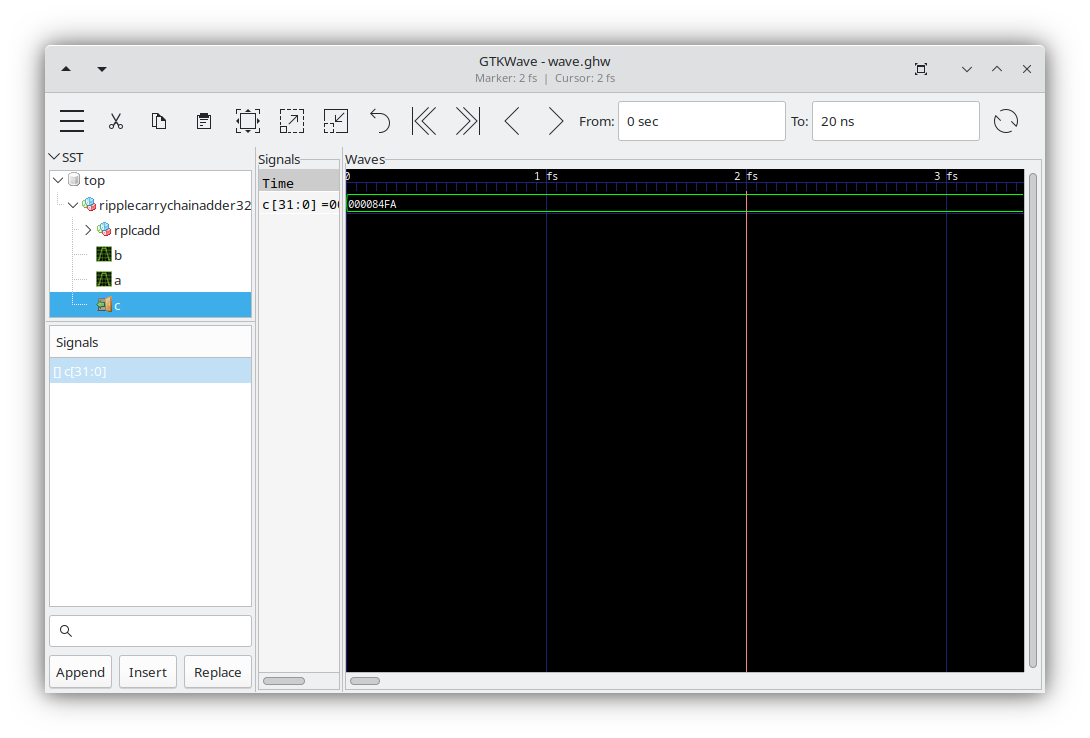

19219 - 14823 = 4396 === 0x112C 14823 - 19219 = -4396 === 0xFFFFFFFFFFFFEED4 |

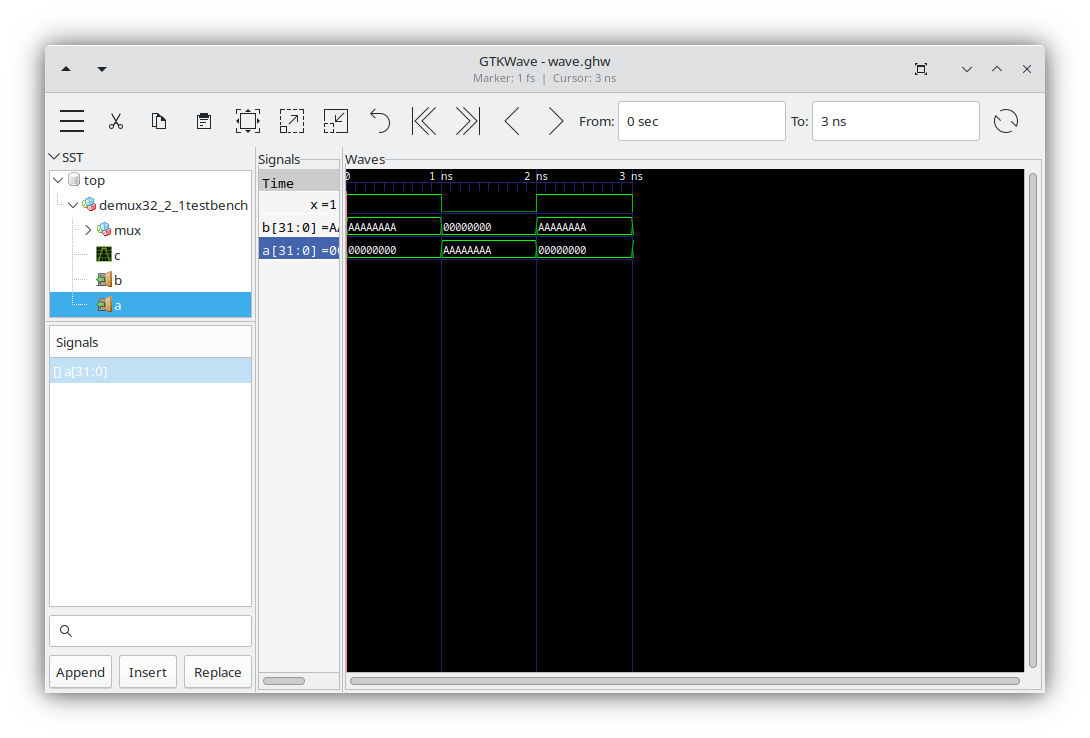

-- (C) David Vajda

-- 32 Bit x 2:1 MUX

-- 2024-12-02

library ieee;

use ieee.std_logic_1164.all;

entity MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end;

architecture behaviour of MUX32_2_1 is

begin

MUX_generate: FOR i IN 31 DOWNTO 0 GENERATE

c (i) <= (a (i) and not x) or (b (i) and x);

END GENERATE;

end;

library ieee;

use ieee.std_logic_1164.all;

entity MUX32_2_1testbench is

port (

c: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of MUX32_2_1testbench is

component MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

signal b: std_logic_vector (31 downto 0);

signal a: std_logic_vector (31 downto 0);

signal x: std_logic;

begin

mux: MUX32_2_1 PORT MAP (c=>c, b=>b, a=>a, x=>x);

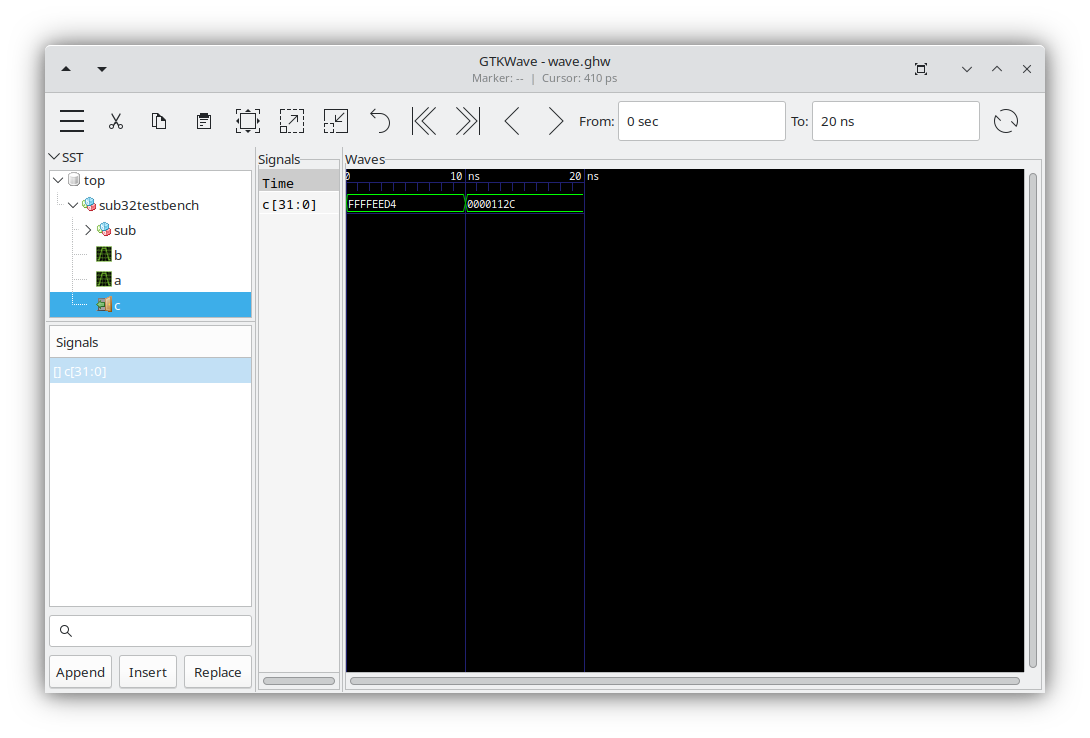

a <= ('1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0');

b <= ('1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0');

x <= '1' after 0 ns, '0' after 1 ns, '1' after 2 ns, '0' after 3 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity DeMUX32_2_1 is

port (

c: in std_logic_vector (31 downto 0);

b: out std_logic_vector (31 downto 0);

a: out std_logic_vector (31 downto 0);

x: in std_logic

);

end;

architecture behaviour of DeMUX32_2_1 is

begin

MUX_generate: FOR i IN 31 DOWNTO 0 GENERATE

a (i) <= (c (i) and not x);

b (i) <= (c (i) and x);

END GENERATE;

end;

library ieee;

use ieee.std_logic_1164.all;

entity DeMUX32_2_1testbench is

port (

a: out std_logic_vector (31 downto 0);

b: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of DeMUX32_2_1testbench is

component DeMUX32_2_1 is

port (

c: in std_logic_vector (31 downto 0);

b: out std_logic_vector (31 downto 0);

a: out std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

signal c: std_logic_vector (31 downto 0);

signal x: std_logic;

begin

mux: DeMUX32_2_1 PORT MAP (c=>c, b=>b, a=>a, x=>x);

c <= ('1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0');

x <= '1' after 0 ns, '0' after 1 ns, '1' after 2 ns, '0' after 3 ns;

end;

|

jetzt kommen 5 kaskadierte MUX

-- (C) David Vajda

-- 32 Bit x 2:1 MUX

-- 2024-12-02

library ieee;

use ieee.std_logic_1164.all;

package MIPS32 is

type bus2_32 is array (1 downto 0) of std_logic_vector (31 downto 0);

type bus4_32 is array (1 downto 0) of std_logic_vector (31 downto 0);

end package;

library ieee;

use ieee.std_logic_1164.all;

library work;

use work.mips32.all;

entity MUX32_2_1 is

port (

b: out std_logic_vector (31 downto 0);

a: in bus2_32;

x: in std_logic

);

end;

architecture behaviour of MUX32_2_1 is

begin

MUX_generate: FOR i IN 31 DOWNTO 0 GENERATE

b (i) <= (a (1)(i) and not x) or (a(0) (i) and x);

END GENERATE;

end;

library ieee;

use ieee.std_logic_1164.all;

library work;

use work.mips32.all;

entity MUX32_4_1 is

port (

b: out std_logic_vector (31 downto 0);

a: in bus4_32;

x: in std_logic

);

end;

architecture behaviour of MUX32_2_1 is

component MUX32_2_1

port (

b: out std_logic_vector (31 downto 0);

a: in bus2_32;

x: in std_logic

);

end component;

begin

MUX_generate: FOR i IN 31 DOWNTO 0 GENERATE

b (i) <= (a (1)(i) and not x) or (a(0) (i) and x);

END GENERATE;

end;

|

-- (C) David Vajda

-- D-FF/32 x 32 Bit Register set MIPS32/2 Src, 1 Dest

-- 2024-11-28/2024-12-04

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end;

architecture behaviour of rslatch is

begin

q <= (r nor p);

p <= (s nor q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch is

component rslatch

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end component;

signal e, d: std_logic;

begin

rs: rslatch PORT MAP (r=>e, s=>d, q=>q);

d <= c and s;

e <= c and r;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch is

component clktriggeredrslatch

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end component;

signal e, f: std_logic;

begin

clkrs: clktriggeredrslatch PORT MAP (r=>f, s=>e, c=>c, q=>q);

e <= d;

f <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatchtestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatchtestbench is

component dlatch

port (

c: in std_logic;

d: in std_logic;

q: inout std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dlatch PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dff is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dff is

component dlatch

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal e, a, b: std_logic;

begin

d1: dlatch PORT MAP (c=>a, d=>e, q=>q);

d2: dlatch PORT MAP (c=>b, d=>d, q=>e);

a <= not c;

b <= c;

end;

library ieee;

use ieee.std_logic_1164.all;

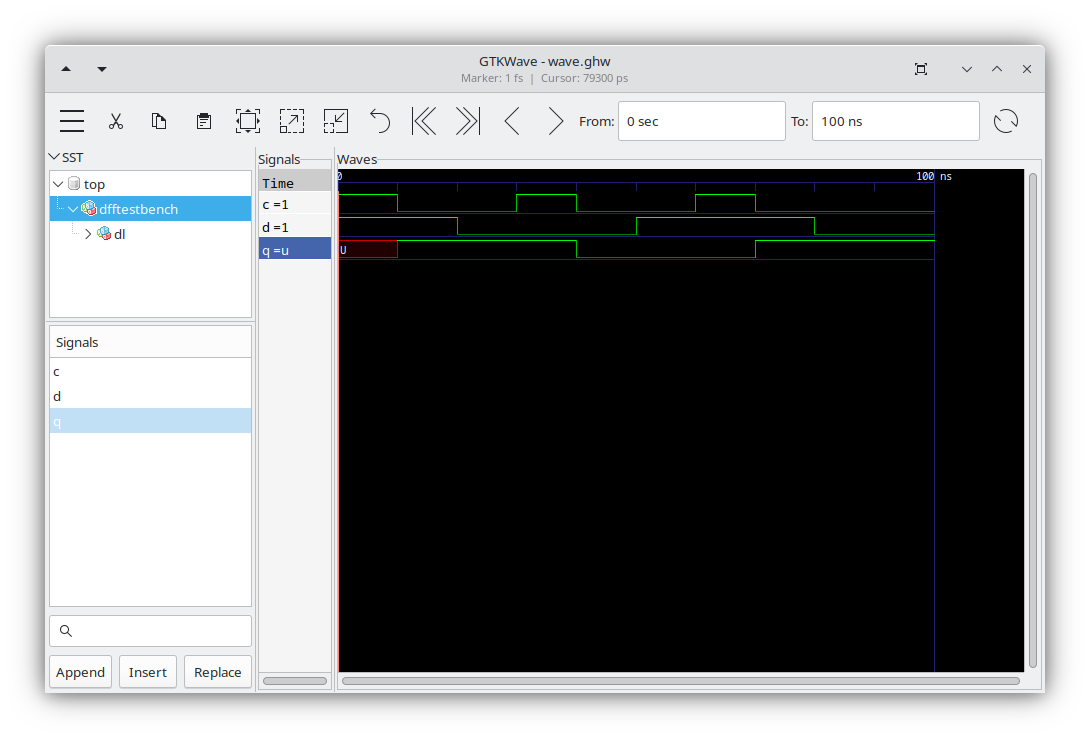

entity dfftestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dfftestbench is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dff PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

|

so weit so gut

-- (C) David Vajda

-- D-FF/32 x 32 Bit Register set MIPS32/2 Src, 1 Dest

-- 2024-11-28/2024-12-04

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end;

architecture behaviour of rslatch is

begin

q <= (r nor p);

p <= (s nor q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch is

component rslatch

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end component;

signal e, d: std_logic;

begin

rs: rslatch PORT MAP (r=>e, s=>d, q=>q);

d <= c and s;

e <= c and r;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch is

component clktriggeredrslatch

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end component;

signal e, f: std_logic;

begin

clkrs: clktriggeredrslatch PORT MAP (r=>f, s=>e, c=>c, q=>q);

e <= d;

f <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatchtestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatchtestbench is

component dlatch

port (

c: in std_logic;

d: in std_logic;

q: inout std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dlatch PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dff is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dff is

component dlatch

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal e, a, b: std_logic;

begin

d1: dlatch PORT MAP (c=>a, d=>e, q=>q);

d2: dlatch PORT MAP (c=>b, d=>d, q=>e);

a <= not c;

b <= c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dfftestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dfftestbench is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dff PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

c: in std_logic;

d: in std_logic_vector (31 downto 0);

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal p: std_logic_vector (31 downto 0);

begin

gen_reg: FOR i in 31 downto 0 generate

dffx: dff PORT MAP (q=>p(i),d=>d(i),c=>c);

q(i) <= p (i);

end generate;

end;

|

-- (C) David Vajda

-- D-FF/32 x 32 Bit Register set MIPS32/2 Src, 1 Dest

-- 2024-11-28/2024-12-04

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end;

architecture behaviour of rslatch is

begin

q <= (r nor p);

p <= (s nor q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch is

component rslatch

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end component;

signal e, d: std_logic;

begin

rs: rslatch PORT MAP (r=>e, s=>d, q=>q);

d <= c and s;

e <= c and r;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch is

component clktriggeredrslatch

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end component;

signal e, f: std_logic;

begin

clkrs: clktriggeredrslatch PORT MAP (r=>f, s=>e, c=>c, q=>q);

e <= d;

f <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatchtestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatchtestbench is

component dlatch

port (

c: in std_logic;

d: in std_logic;

q: inout std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dlatch PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dff is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dff is

component dlatch

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal e, a, b: std_logic;

begin

d1: dlatch PORT MAP (c=>a, d=>e, q=>q);

d2: dlatch PORT MAP (c=>b, d=>d, q=>e);

a <= not c;

b <= c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dfftestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dfftestbench is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dff PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

c: in std_logic;

d: in std_logic_vector (31 downto 0);

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal p: std_logic_vector (31 downto 0);

begin

gen_reg: FOR i in 31 downto 0 generate

dffx: dff PORT MAP (q=>p(i),d=>d(i),c=>c);

q(i) <= p (i);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

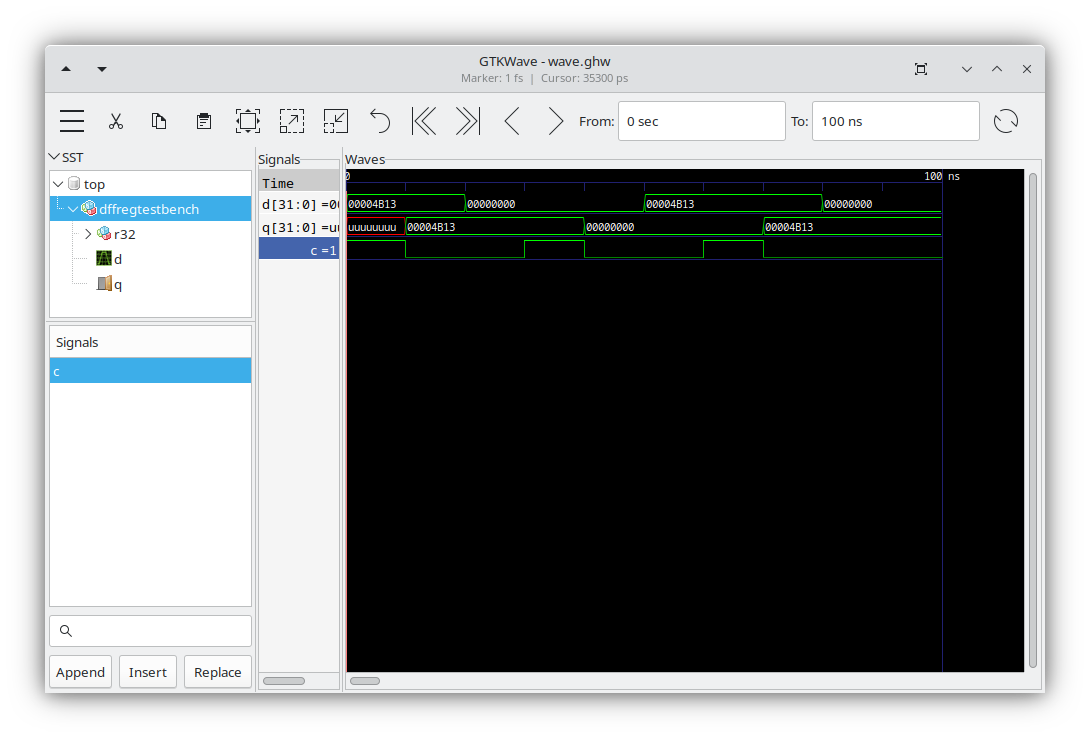

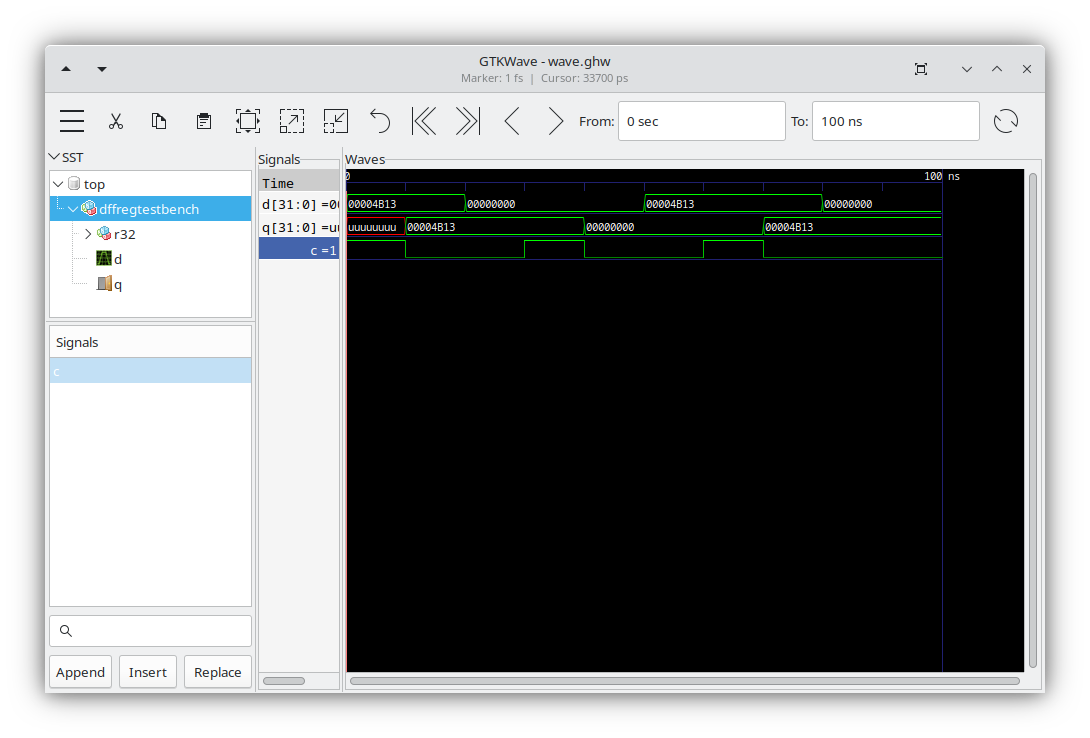

entity dffregtestbench is

port (

q: inout std_logic_vector (31 downto 0)

);

end;

architecture behaviour of dffregtestbench is

component reg32

port (

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0);

c: in std_logic

);

end component;

signal d: std_logic_vector (31 downto 0);

signal c: std_logic;

begin

r32: reg32 PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 10 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 20 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 30 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 40 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 50 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 60 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 70 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 80 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 90 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

|

library ieee;

use ieee.std_logic_1164.all;

entity registerset2_32 is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic_vector (4 downto 0);

regsrc2: in std_logic_vector (4 downto 0);

regdest: in std_logic_vector (4 downto 0);

en: in std_logic;

);

end;

|

library ieee;

use ieee.std_logic_1164.all;

entity registerset2_32 is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic;

regsrc2: in std_logic;

regdest: in std_logic;

en: in std_logic

);

end;

architecture behaviour of registerset2_32 is

component reg32

port (

c: in std_logic;

d: in std_logic_vector (31 downto 0);

q: out std_logic_vector (31 downto 0)

);

end component;

component MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

signal q1: std_logic_vector (31 downto 0);

signal q2: std_logic_vector (31 downto 0);

signal c1, c2: std_logic;

begin

reg1: reg32 PORT MAP (q=>q1,d=>destdata,c=>c1);

reg2: reg32 PORT MAP (q=>q2,d=>destdata,c=>c2);

srcmux1: MUX32_2_1 PORT MAP (a=>q1, b=>q2, c=>srcdata1, x=>regsrc1);

srcmux2: MUX32_2_1 PORT MAP (a=>q1, b=>q2, c=>srcdata2, x=>regsrc2);

c1 <= en and regdest;

c2 <= en and not regdest;

end;

|

-- (C) David Vajda

-- D-FF/32 x 32 Bit Register set MIPS32/2 Src, 1 Dest

-- 2024-11-28/2024-12-04

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end;

architecture behaviour of rslatch is

begin

q <= (r nor p);

p <= (s nor q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch is

component rslatch

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end component;

signal e, d: std_logic;

begin

rs: rslatch PORT MAP (r=>e, s=>d, q=>q);

d <= c and s;

e <= c and r;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch is

component clktriggeredrslatch

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end component;

signal e, f: std_logic;

begin

clkrs: clktriggeredrslatch PORT MAP (r=>f, s=>e, c=>c, q=>q);

e <= d;

f <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatchtestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatchtestbench is

component dlatch

port (

c: in std_logic;

d: in std_logic;

q: inout std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dlatch PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dff is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dff is

component dlatch

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal e, a, b: std_logic;

begin

d1: dlatch PORT MAP (c=>a, d=>e, q=>q);

d2: dlatch PORT MAP (c=>b, d=>d, q=>e);

a <= not c;

b <= c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dfftestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dfftestbench is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dff PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

c: in std_logic;

d: in std_logic_vector (31 downto 0);

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal p: std_logic_vector (31 downto 0);

begin

gen_reg: FOR i in 31 downto 0 generate

dffx: dff PORT MAP (q=>p(i),d=>d(i),c=>c);

q(i) <= p (i);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dffregtestbench is

port (

q: inout std_logic_vector (31 downto 0)

);

end;

architecture behaviour of dffregtestbench is

component reg32

port (

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0);

c: in std_logic

);

end component;

signal d: std_logic_vector (31 downto 0);

signal c: std_logic;

begin

r32: reg32 PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 10 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 20 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 30 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 40 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 50 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 60 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 70 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 80 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 90 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end;

architecture behaviour of MUX32_2_1 is

begin

MUX_generate: FOR i IN 31 DOWNTO 0 GENERATE

c (i) <= (a (i) and not x) or (b (i) and x);

END GENERATE;

end;

library ieee;

use ieee.std_logic_1164.all;

entity MUX32_2_1testbench is

port (

c: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of MUX32_2_1testbench is

component MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

signal b: std_logic_vector (31 downto 0);

signal a: std_logic_vector (31 downto 0);

signal x: std_logic;

begin

mux: MUX32_2_1 PORT MAP (c=>c, b=>b, a=>a, x=>x);

a <= ('1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0');

b <= ('1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0');

x <= '1' after 0 ns, '0' after 1 ns, '1' after 2 ns, '0' after 3 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset2_32 is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic;

regsrc2: in std_logic;

regdest: in std_logic;

en: in std_logic

);

end;

architecture behaviour of registerset2_32 is

component reg32

port (

c: in std_logic;

d: in std_logic_vector (31 downto 0);

q: out std_logic_vector (31 downto 0)

);

end component;

component MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

signal q1: std_logic_vector (31 downto 0);

signal q2: std_logic_vector (31 downto 0);

signal c1, c2: std_logic;

begin

reg1: reg32 PORT MAP (q=>q1,d=>destdata,c=>c1);

reg2: reg32 PORT MAP (q=>q2,d=>destdata,c=>c2);

srcmux1: MUX32_2_1 PORT MAP (a=>q1, b=>q2, c=>srcdata1, x=>regsrc1);

srcmux2: MUX32_2_1 PORT MAP (a=>q1, b=>q2, c=>srcdata2, x=>regsrc2);

c1 <= en and regdest;

c2 <= en and not regdest;

end;

|

-- (C) David Vajda

-- D-FF/32 x 32 Bit Register set MIPS32/2 Src, 1 Dest

-- 2024-11-28/2024-12-04

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end;

architecture behaviour of rslatch is

begin

q <= (r nor p);

p <= (s nor q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch is

component rslatch

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end component;

signal e, d: std_logic;

begin

rs: rslatch PORT MAP (r=>e, s=>d, q=>q);

d <= c and s;

e <= c and r;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch is

component clktriggeredrslatch

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end component;

signal e, f: std_logic;

begin

clkrs: clktriggeredrslatch PORT MAP (r=>f, s=>e, c=>c, q=>q);

e <= d;

f <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatchtestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatchtestbench is

component dlatch

port (

c: in std_logic;

d: in std_logic;

q: inout std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dlatch PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dff is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dff is

component dlatch

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal e, a, b: std_logic;

begin

d1: dlatch PORT MAP (c=>a, d=>e, q=>q);

d2: dlatch PORT MAP (c=>b, d=>d, q=>e);

a <= not c;

b <= c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dfftestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dfftestbench is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dff PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

c: in std_logic;

d: in std_logic_vector (31 downto 0);

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal p: std_logic_vector (31 downto 0);

begin

gen_reg: FOR i in 31 downto 0 generate

dffx: dff PORT MAP (q=>p(i),d=>d(i),c=>c);

q(i) <= p (i);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dffregtestbench is

port (

q: inout std_logic_vector (31 downto 0)

);

end;

architecture behaviour of dffregtestbench is

component reg32

port (

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0);

c: in std_logic

);

end component;

signal d: std_logic_vector (31 downto 0);

signal c: std_logic;

begin

r32: reg32 PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 10 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 20 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 30 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 40 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 50 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 60 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 70 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 80 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 90 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end;

architecture behaviour of MUX32_2_1 is

begin

MUX_generate: FOR i IN 31 DOWNTO 0 GENERATE

c (i) <= (a (i) and not x) or (b (i) and x);

END GENERATE;

end;

library ieee;

use ieee.std_logic_1164.all;

entity MUX32_2_1testbench is

port (

c: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of MUX32_2_1testbench is

component MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

signal b: std_logic_vector (31 downto 0);

signal a: std_logic_vector (31 downto 0);

signal x: std_logic;

begin

mux: MUX32_2_1 PORT MAP (c=>c, b=>b, a=>a, x=>x);

a <= ('1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0');

b <= ('1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0');

x <= '1' after 0 ns, '0' after 1 ns, '1' after 2 ns, '0' after 3 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset2_32 is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic;

regsrc2: in std_logic;

regdest: in std_logic;

en: in std_logic

);

end;

architecture behaviour of registerset2_32 is

component reg32

port (

c: in std_logic;

d: in std_logic_vector (31 downto 0);

q: out std_logic_vector (31 downto 0)

);

end component;

component MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

signal q1: std_logic_vector (31 downto 0);

signal q2: std_logic_vector (31 downto 0);

signal c1, c2: std_logic;

begin

reg1: reg32 PORT MAP (q=>q1,d=>destdata,c=>c1);

reg2: reg32 PORT MAP (q=>q2,d=>destdata,c=>c2);

srcmux1: MUX32_2_1 PORT MAP (a=>q1, b=>q2, c=>srcdata1, x=>regsrc1);

srcmux2: MUX32_2_1 PORT MAP (a=>q1, b=>q2, c=>srcdata2, x=>regsrc2);

c1 <= en and not regdest;

c2 <= en and regdest;

end;

library ieee;

use ieee.std_logic_1164.all;

-- use std.textio.all;

-- use ieee.std_logic_textio.all;

entity registerset2_32testbench is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of registerset2_32testbench is

component registerset2_32

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic;

regsrc2: in std_logic;

regdest: in std_logic;

en: in std_logic

);

end component;

signal destdata: std_logic_vector (31 downto 0);

signal regsrc1: std_logic;

signal regsrc2: std_logic;

signal regdest: std_logic;

signal en: std_logic;

begin

regset_2_32: registerset2_32 PORT MAP (srcdata1=>srcdata1, srcdata2=>srcdata2, destdata=>destdata, regsrc1=>regsrc1, regsrc2=>regsrc2, regdest=>regdest, en=>en);

regdest <= '0' after 0 ns;

destdata <= ('1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 30 ns;

en <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns;

regdest <= '0' after 0 ns;

regsrc1 <= '0' after 0 ns;

regsrc2 <= '0' after 0 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset4_32 is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic_vector (1 downto 0);

regsrc2: in std_logic_vector (1 downto 0);

regdest: in std_logic_vector (1 downto 0);

en: in std_logic

);

end;

architecture behaviour of registerset4_32 is

component MUX32_2_1

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

component registerset2_32

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic;

regsrc2: in std_logic;

regdest: in std_logic;

en: in std_logic

);

end component;

signal c1, c2: std_logic;

signal en1, en2: std_logic;

signal srcdata1_1: std_logic_vector (31 downto 0);

signal srcdata1_2: std_logic_vector (31 downto 0);

signal srcdata2_1: std_logic_vector (31 downto 0);

signal srcdata2_2: std_logic_vector (31 downto 0);

begin

mux1: MUX32_2_1 PORT MAP (a=>srcdata1_1, b=>srcdata1_2, c=>srcdata1, x=>regsrc1 (1));

mux2: MUX32_2_1 PORT MAP (a=>srcdata2_1, b=>srcdata2_2, c=>srcdata2, x=>regsrc2 (1));

reg1: registerset2_32 PORT MAP (srcdata1=>srcdata1_1, srcdata2=>srcdata2_1, regsrc1=>regsrc1 (0), regsrc2=>regsrc2 (0), en=>en1, destdata=>destdata, regdest=>regdest (0));

reg2: registerset2_32 PORT MAP (srcdata1=>srcdata1_2, srcdata2=>srcdata2_2, regsrc1=>regsrc1 (0), regsrc2=>regsrc2 (0), en=>en2, destdata=>destdata, regdest=>regdest (0));

en2 <= regdest (1) and en;

en1 <= not regdest (1) and en;

end;

library ieee;

use ieee.std_logic_1164.all;

-- use std.textio.all;

-- use ieee.std_logic_textio.all;

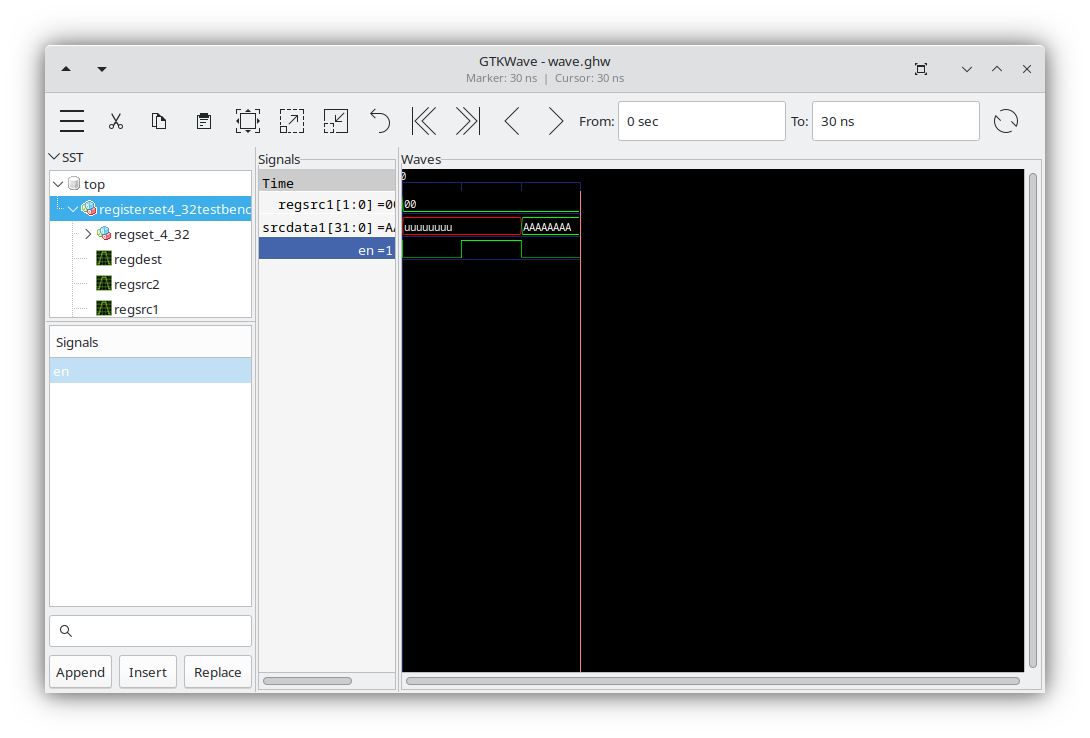

entity registerset4_32testbench is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of registerset4_32testbench is

component registerset4_32

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic_vector (1 downto 0);

regsrc2: in std_logic_vector (1 downto 0);

regdest: in std_logic_vector (1 downto 0);

en: in std_logic

);

end component;

signal destdata: std_logic_vector (31 downto 0);

signal regsrc1: std_logic_vector (1 downto 0);

signal regsrc2: std_logic_vector (1 downto 0);

signal regdest: std_logic_vector (1 downto 0);

signal en: std_logic;

begin

regset_4_32: registerset4_32 PORT MAP (srcdata1=>srcdata1, srcdata2=>srcdata2, destdata=>destdata, regsrc1=>regsrc1, regsrc2=>regsrc2, regdest=>regdest, en=>en);

regdest <= ('0','0') after 0 ns;

destdata <= ('1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 30 ns;

en <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns;

regdest <= ('0','0') after 0 ns;

regsrc1 <= ('0','0') after 0 ns;

regsrc2 <= ('0','0') after 0 ns;

end;

|

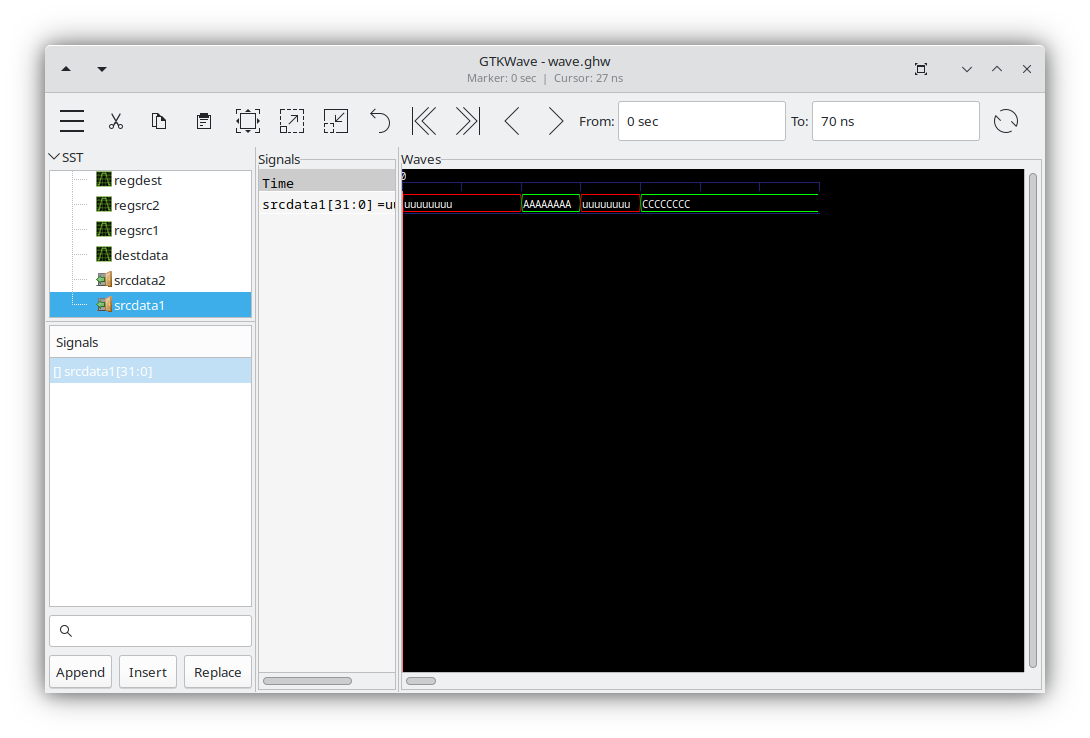

library ieee;

use ieee.std_logic_1164.all;

entity registerset2_32 is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic;

regsrc2: in std_logic;

regdest: in std_logic;

en: in std_logic

);

end;

architecture behaviour of registerset2_32 is

component reg32

port (

c: in std_logic;

d: in std_logic_vector (31 downto 0);

q: out std_logic_vector (31 downto 0)

);

end component;

component MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

signal q1: std_logic_vector (31 downto 0);

signal q2: std_logic_vector (31 downto 0);

signal c1, c2: std_logic;

begin

reg1: reg32 PORT MAP (q=>q1,d=>destdata,c=>c1);

reg2: reg32 PORT MAP (q=>q2,d=>destdata,c=>c2);

srcmux1: MUX32_2_1 PORT MAP (a=>q1, b=>q2, c=>srcdata1, x=>regsrc1);

srcmux2: MUX32_2_1 PORT MAP (a=>q1, b=>q2, c=>srcdata2, x=>regsrc2);

c1 <= en and not regdest;

c2 <= en and regdest;

end;

library ieee;

use ieee.std_logic_1164.all;

-- use std.textio.all;

-- use ieee.std_logic_textio.all;

-- ...

library ieee;

use ieee.std_logic_1164.all;

entity registerset4_32 is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic_vector (1 downto 0);

regsrc2: in std_logic_vector (1 downto 0);

regdest: in std_logic_vector (1 downto 0);

en: in std_logic

);

end;

architecture behaviour of registerset4_32 is

component MUX32_2_1

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

component registerset2_32

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic;

regsrc2: in std_logic;

regdest: in std_logic;

en: in std_logic

);

end component;

signal c1, c2: std_logic;

signal en1, en2: std_logic;

signal srcdata1_1: std_logic_vector (31 downto 0);

signal srcdata1_2: std_logic_vector (31 downto 0);

signal srcdata2_1: std_logic_vector (31 downto 0);

signal srcdata2_2: std_logic_vector (31 downto 0);

begin

mux1: MUX32_2_1 PORT MAP (a=>srcdata1_1, b=>srcdata1_2, c=>srcdata1, x=>regsrc1 (1));

mux2: MUX32_2_1 PORT MAP (a=>srcdata2_1, b=>srcdata2_2, c=>srcdata2, x=>regsrc2 (1));

reg1: registerset2_32 PORT MAP (srcdata1=>srcdata1_1, srcdata2=>srcdata2_1, regsrc1=>regsrc1 (0), regsrc2=>regsrc2 (0), en=>en1, destdata=>destdata, regdest=>regdest (0));

reg2: registerset2_32 PORT MAP (srcdata1=>srcdata1_2, srcdata2=>srcdata2_2, regsrc1=>regsrc1 (0), regsrc2=>regsrc2 (0), en=>en2, destdata=>destdata, regdest=>regdest (0));

en2 <= regdest (1) and en;

en1 <= not regdest (1) and en;

end;

library ieee;

use ieee.std_logic_1164.all;

-- use std.textio.all;

-- use ieee.std_logic_textio.all;

entity registerset4_32testbench is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of registerset4_32testbench is

component registerset4_32

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic_vector (1 downto 0);

regsrc2: in std_logic_vector (1 downto 0);

regdest: in std_logic_vector (1 downto 0);

en: in std_logic

);

end component;

signal destdata: std_logic_vector (31 downto 0);

signal regsrc1: std_logic_vector (1 downto 0);

signal regsrc2: std_logic_vector (1 downto 0);

signal regdest: std_logic_vector (1 downto 0);

signal en: std_logic;

begin

regset_4_32: registerset4_32 PORT MAP (srcdata1=>srcdata1, srcdata2=>srcdata2, destdata=>destdata, regsrc1=>regsrc1, regsrc2=>regsrc2, regdest=>regdest, en=>en);

regdest <= ('0','0') after 0 ns;

destdata <= ('1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 30 ns;

en <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns;

regdest <= ('0','0') after 0 ns;

regsrc1 <= ('0','0') after 0 ns;

regsrc2 <= ('0','0') after 0 ns;

end;

|

-- (C) David Vajda

-- D-FF/32 x 32 Bit Register set MIPS32/2 Src, 1 Dest

-- 2024-11-28/2024-12-04

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end;

architecture behaviour of rslatch is

begin

q <= (r nor p);

p <= (s nor q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch is

component rslatch

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end component;

signal e, d: std_logic;

begin

rs: rslatch PORT MAP (r=>e, s=>d, q=>q);

d <= c and s;

e <= c and r;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch is

component clktriggeredrslatch

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end component;

signal e, f: std_logic;

begin

clkrs: clktriggeredrslatch PORT MAP (r=>f, s=>e, c=>c, q=>q);

e <= d;

f <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatchtestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatchtestbench is

component dlatch

port (

c: in std_logic;

d: in std_logic;

q: inout std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dlatch PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dff is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dff is

component dlatch

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal e, a, b: std_logic;

begin

d1: dlatch PORT MAP (c=>a, d=>e, q=>q);

d2: dlatch PORT MAP (c=>b, d=>d, q=>e);

a <= not c;

b <= c;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dfftestbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dfftestbench is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dff PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

c: in std_logic;

d: in std_logic_vector (31 downto 0);

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dff

port (

q: inout std_logic;

d: in std_logic;

c: in std_logic

);

end component;

signal p: std_logic_vector (31 downto 0);

begin

gen_reg: FOR i in 31 downto 0 generate

dffx: dff PORT MAP (q=>p(i),d=>d(i),c=>c);

q(i) <= p (i);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dffregtestbench is

port (

q: inout std_logic_vector (31 downto 0)

);

end;

architecture behaviour of dffregtestbench is

component reg32

port (

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0);

c: in std_logic

);

end component;

signal d: std_logic_vector (31 downto 0);

signal c: std_logic;

begin

r32: reg32 PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 10 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 20 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 30 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 40 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 50 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 60 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','1','0','0', '1','0','1','1', '0','0','0','1' ,'0','0','1','1') after 70 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 80 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 90 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end;

architecture behaviour of MUX32_2_1 is

begin

MUX_generate: FOR i IN 31 DOWNTO 0 GENERATE

c (i) <= (a (i) and not x) or (b (i) and x);

END GENERATE;

end;

library ieee;

use ieee.std_logic_1164.all;

entity MUX32_2_1testbench is

port (

c: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of MUX32_2_1testbench is

component MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

signal b: std_logic_vector (31 downto 0);

signal a: std_logic_vector (31 downto 0);

signal x: std_logic;

begin

mux: MUX32_2_1 PORT MAP (c=>c, b=>b, a=>a, x=>x);

a <= ('1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0');

b <= ('1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0');

x <= '1' after 0 ns, '0' after 1 ns, '1' after 2 ns, '0' after 3 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset2_32 is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic;

regsrc2: in std_logic;

regdest: in std_logic;

en: in std_logic

);

end;

architecture behaviour of registerset2_32 is

component reg32

port (

c: in std_logic;

d: in std_logic_vector (31 downto 0);

q: out std_logic_vector (31 downto 0)

);

end component;

component MUX32_2_1 is

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

signal q1: std_logic_vector (31 downto 0);

signal q2: std_logic_vector (31 downto 0);

signal c1, c2: std_logic;

begin

reg1: reg32 PORT MAP (q=>q1,d=>destdata,c=>c1);

reg2: reg32 PORT MAP (q=>q2,d=>destdata,c=>c2);

srcmux1: MUX32_2_1 PORT MAP (a=>q1, b=>q2, c=>srcdata1, x=>regsrc1);

srcmux2: MUX32_2_1 PORT MAP (a=>q1, b=>q2, c=>srcdata2, x=>regsrc2);

c1 <= en and not regdest;

c2 <= en and regdest;

end;

library ieee;

use ieee.std_logic_1164.all;

-- use std.textio.all;

-- use ieee.std_logic_textio.all;

entity registerset2_32testbench is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of registerset2_32testbench is

component registerset2_32

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic;

regsrc2: in std_logic;

regdest: in std_logic;

en: in std_logic

);

end component;

signal destdata: std_logic_vector (31 downto 0);

signal regsrc1: std_logic;

signal regsrc2: std_logic;

signal regdest: std_logic;

signal en: std_logic;

begin

regset_2_32: registerset2_32 PORT MAP (srcdata1=>srcdata1, srcdata2=>srcdata2, destdata=>destdata, regsrc1=>regsrc1, regsrc2=>regsrc2, regdest=>regdest, en=>en);

regdest <= '0' after 0 ns;

destdata <= ('1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 30 ns;

en <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns;

regdest <= '0' after 0 ns;

regsrc1 <= '0' after 0 ns;

regsrc2 <= '0' after 0 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset4_32 is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic_vector (1 downto 0);

regsrc2: in std_logic_vector (1 downto 0);

regdest: in std_logic_vector (1 downto 0);

en: in std_logic

);

end;

architecture behaviour of registerset4_32 is

component MUX32_2_1

port (

c: out std_logic_vector (31 downto 0);

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

x: in std_logic

);

end component;

component registerset2_32

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic;

regsrc2: in std_logic;

regdest: in std_logic;

en: in std_logic

);

end component;

signal c1, c2: std_logic;

signal en1, en2: std_logic;

signal srcdata1_1: std_logic_vector (31 downto 0);

signal srcdata1_2: std_logic_vector (31 downto 0);

signal srcdata2_1: std_logic_vector (31 downto 0);

signal srcdata2_2: std_logic_vector (31 downto 0);

begin

mux1: MUX32_2_1 PORT MAP (a=>srcdata1_1, b=>srcdata1_2, c=>srcdata1, x=>regsrc1 (1));

mux2: MUX32_2_1 PORT MAP (a=>srcdata2_1, b=>srcdata2_2, c=>srcdata2, x=>regsrc2 (1));

reg1: registerset2_32 PORT MAP (srcdata1=>srcdata1_1, srcdata2=>srcdata2_1, regsrc1=>regsrc1 (0), regsrc2=>regsrc2 (0), en=>en1, destdata=>destdata, regdest=>regdest (0));

reg2: registerset2_32 PORT MAP (srcdata1=>srcdata1_2, srcdata2=>srcdata2_2, regsrc1=>regsrc1 (0), regsrc2=>regsrc2 (0), en=>en2, destdata=>destdata, regdest=>regdest (0));

en2 <= regdest (1) and en;

en1 <= not regdest (1) and en;

end;

library ieee;

use ieee.std_logic_1164.all;

-- use std.textio.all;

-- use ieee.std_logic_textio.all;

entity registerset4_32testbench is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of registerset4_32testbench is

component registerset4_32

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic_vector (1 downto 0);

regsrc2: in std_logic_vector (1 downto 0);

regdest: in std_logic_vector (1 downto 0);

en: in std_logic

);

end component;

signal destdata: std_logic_vector (31 downto 0);

signal regsrc1: std_logic_vector (1 downto 0);

signal regsrc2: std_logic_vector (1 downto 0);

signal regdest: std_logic_vector (1 downto 0);

signal en: std_logic;

begin

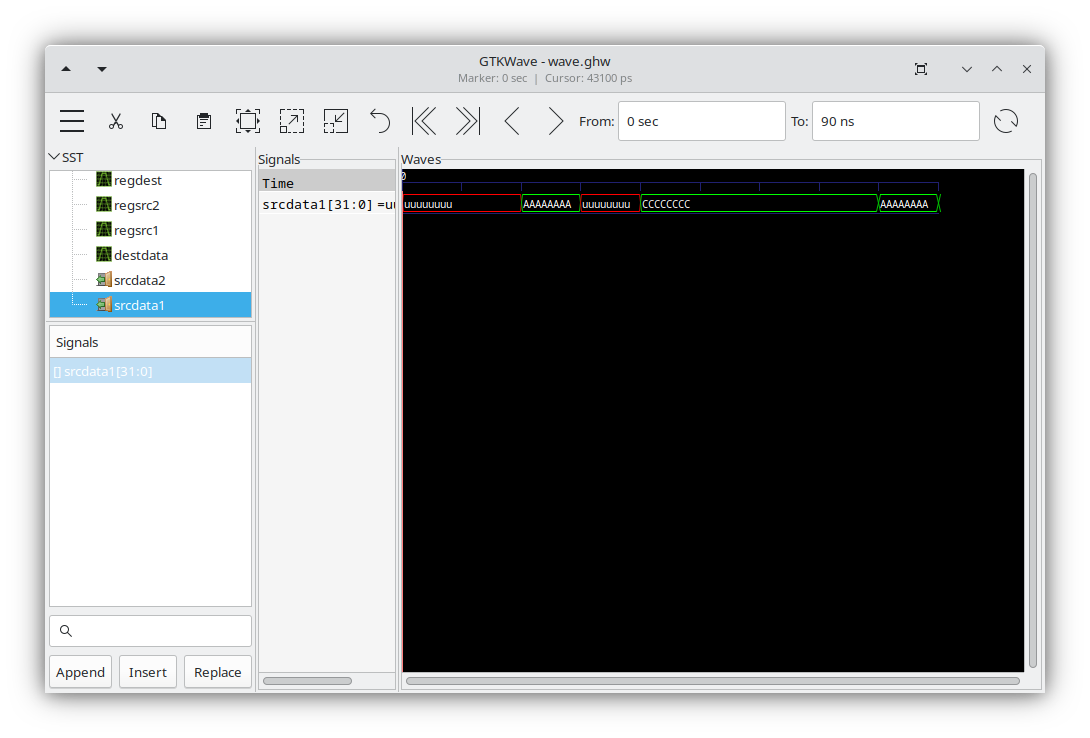

regset_4_32: registerset4_32 PORT MAP (srcdata1=>srcdata1, srcdata2=>srcdata2, destdata=>destdata, regsrc1=>regsrc1, regsrc2=>regsrc2, regdest=>regdest, en=>en);

-- regdest <= ('0','0') after 0 ns;

destdata <= ('1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0', '1', '0') after 0 ns, ('0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0', '0','0','0','0' ,'0','0','0','0') after 30 ns, ('1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0', '1', '1', '0', '0') after 40 ns, ('1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1', '1') after 80 ns;

en <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 90 ns, '1' after 110 ns, '0' after 120 ns;

regdest <= ('0','0') after 0 ns, ('0','1') after 30 ns, ('1', '0') after 100 ns;

regsrc1 <= ('0','0') after 0 ns, ('0','1') after 30 ns, ('0','0') after 80 ns, ('0', '1') after 90 ns, ('1', '0') after 110 ns, ('0', '1') after 130 ns, ('1', '0') after 140 ns;

regsrc2 <= ('0','0') after 0 ns, ('0','1') after 30 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset8_32 is

port (

srcdata1: out std_logic_vector (31 downto 0);

srcdata2: out std_logic_vector (31 downto 0);

destdata: in std_logic_vector (31 downto 0);

regsrc1: in std_logic_vector (2 downto 0);

regsrc2: in std_logic_vector (2 downto 0);

regdest: in std_logic_vector (2 downto 0);

en: in std_logic

);

end;

architecture behaviour of registerset8_32 is

component MUX32_2_1

port (

c: out std_logic_vector (31 downto 0);