Nächste Seite: 2024-11-15, Quine Mc Cluskey Aufwärts: Übungen Vorherige Seite: Rechnen II

library ieee; use ieee.std_logic_1164.all; -- the begin

the next

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20241114 is

port(

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

ich vermute es geht so, übersetzen liess es sich

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20241114 is

port(

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rslatch20241114 is

begin

q <= r nor qs;

qs <= s nor q;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch20241114 is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch20241114 is

component rslatch20241114

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal clkr, clks: std_logic;

begin

rs: rslatch20241114 PORT MAP (r=>clkr, s=>clks, q=>q, qs=>qs);

clkr <= c and r;

clks <= c and s;

end;

Später zeigt, sich, noch ist ein Fehler drin

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20241114 is

port(

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rslatch20241114 is

begin

q <= r nor qs;

qs <= s nor q;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch20241114 is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch20241114 is

component rslatch20241114

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal clkr, clks: std_logic;

begin

rs: rslatch20241114 PORT MAP (r=>clkr, s=>clks, q=>q, qs=>qs);

clkr <= c and r;

clks <= c and s;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114 is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114 is

component clktriggeredrslatch20241114

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal ds, dr: std_logic;

begin

clkrs: clktriggeredrslatch20241114 PORT MAP (r=>dr, s=>ds, c=>c, q=>q);

dr <= d;

ds <= not d;

end;

Jetzt der Witz

-- es hat funktioniert!

-- setzzeit und besonders haltezeit nicht vergessen!

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20241114 is

port(

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rslatch20241114 is

begin

q <= r nor qs;

qs <= s nor q;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch20241114 is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch20241114 is

component rslatch20241114

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal clkr, clks: std_logic;

begin

rs: rslatch20241114 PORT MAP (r=>clkr, s=>clks, q=>q, qs=>qs);

clkr <= c and r;

clks <= c and s;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114 is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114 is

component clktriggeredrslatch20241114

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal ds, dr: std_logic;

begin

clkrs: clktriggeredrslatch20241114 PORT MAP (r=>dr, s=>ds, c=>c, q=>q);

dr <= d;

ds <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114testbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114testbench is

component dlatch2024114

port (

q: inout std_logic;

c: in std_logic;

d: in std_logic

);

end component;

signal c, d: std_logic;

begin

dl: dlatch2024114 PORT MAP (d=>d, c=>c, q=>q);

d <= '0' after 0 ns, '1' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '0' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns;

c <= '0' after 0 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '0' after 70 ns;

end;

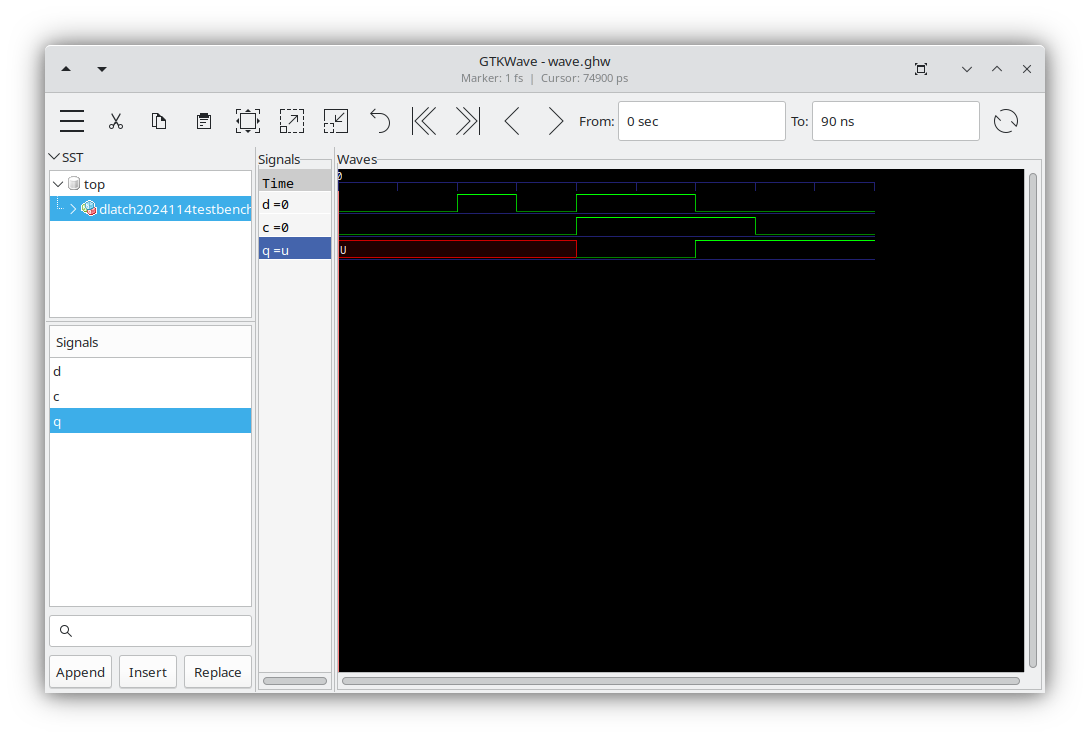

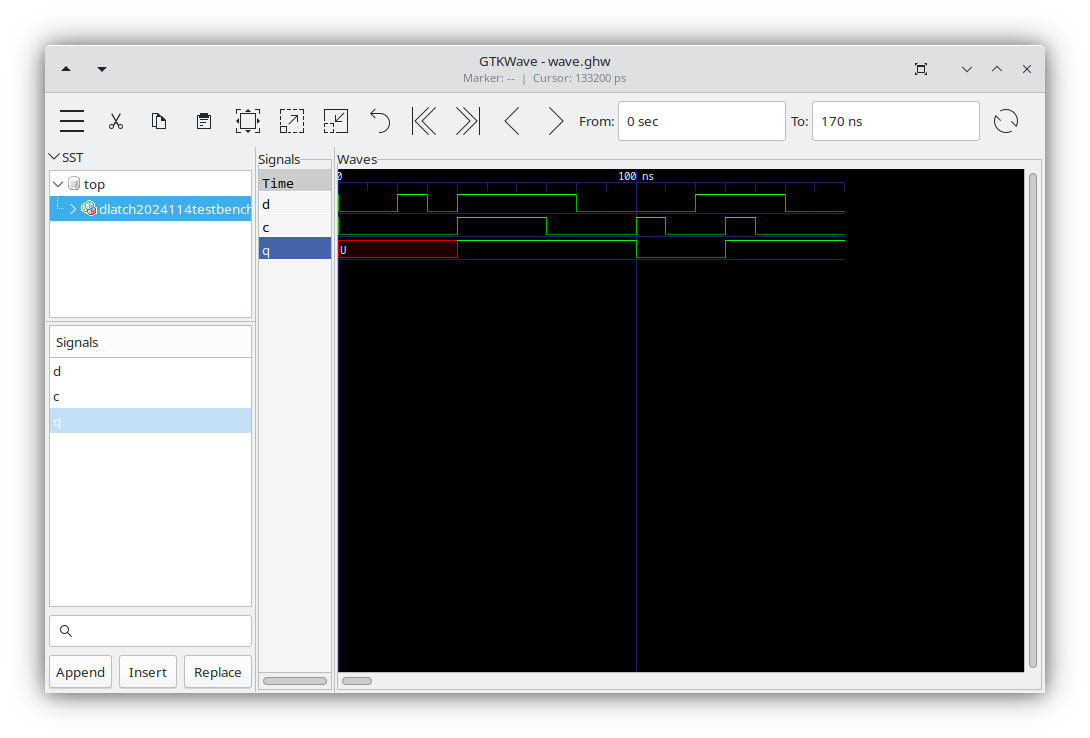

nein, es hat noch einen bug. Aber, was hier als erstes absurd aussieht, ist es nicht. es ist nicht der erste buckel an dem ich mich störe. Hier geht das Datensignal bereits runter, wo der Takt noch da ist. aber das RS-Latch innen drin übernimmt den Zustand - hier wäre die Setzzeit entscheidend - die Haltezeit spielt keine Rolle. Das RS-Latch nimmt den Zustand an, den es beim Beginn des Taktes eingespeist bekommt. Die haltezeit spielt keine Rolle Leider ist das Latch nicht wieder in die andere Richtung gekippt, ich suche den Fehler.

-- so fehler gefunden darf ich vorstellen

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20241114 is

port(

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rslatch20241114 is

begin

q <= r nor qs;

qs <= s nor q;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch20241114 is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch20241114 is

component rslatch20241114

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal clkr, clks: std_logic;

begin

rs: rslatch20241114 PORT MAP (r=>clkr, s=>clks, q=>q, qs=>qs);

clkr <= c and r;

clks <= c and s;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114 is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114 is

component clktriggeredrslatch20241114

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal ds, dr: std_logic;

begin

clkrs: clktriggeredrslatch20241114 PORT MAP (r=>dr, s=>ds, c=>c, q=>q);

dr <= not d;

ds <= d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114testbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114testbench is

component dlatch2024114

port (

q: inout std_logic;

c: in std_logic;

d: in std_logic

);

end component;

signal c, d: std_logic;

begin

dl: dlatch2024114 PORT MAP (d=>d, c=>c, q=>q);

d <= '0' after 0 ns, '1' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns;

c <= '0' after 0 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '0' after 70 ns, '1' after 100 ns, '0' after 110 ns, '0' after 120 ns;

end;

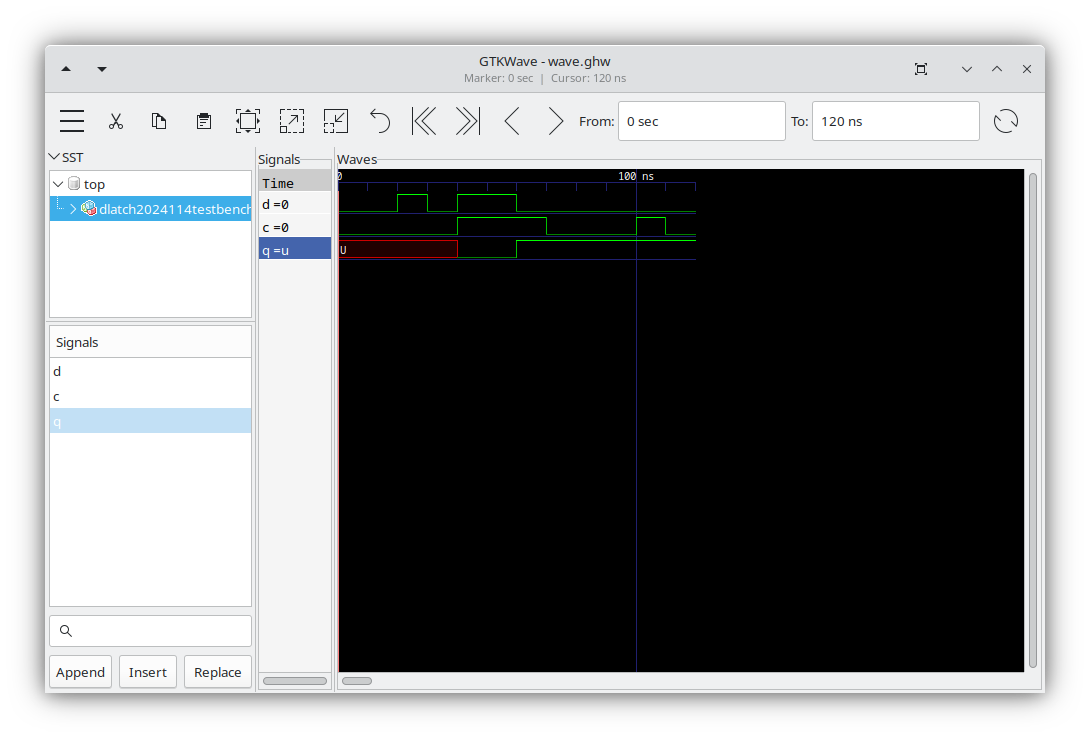

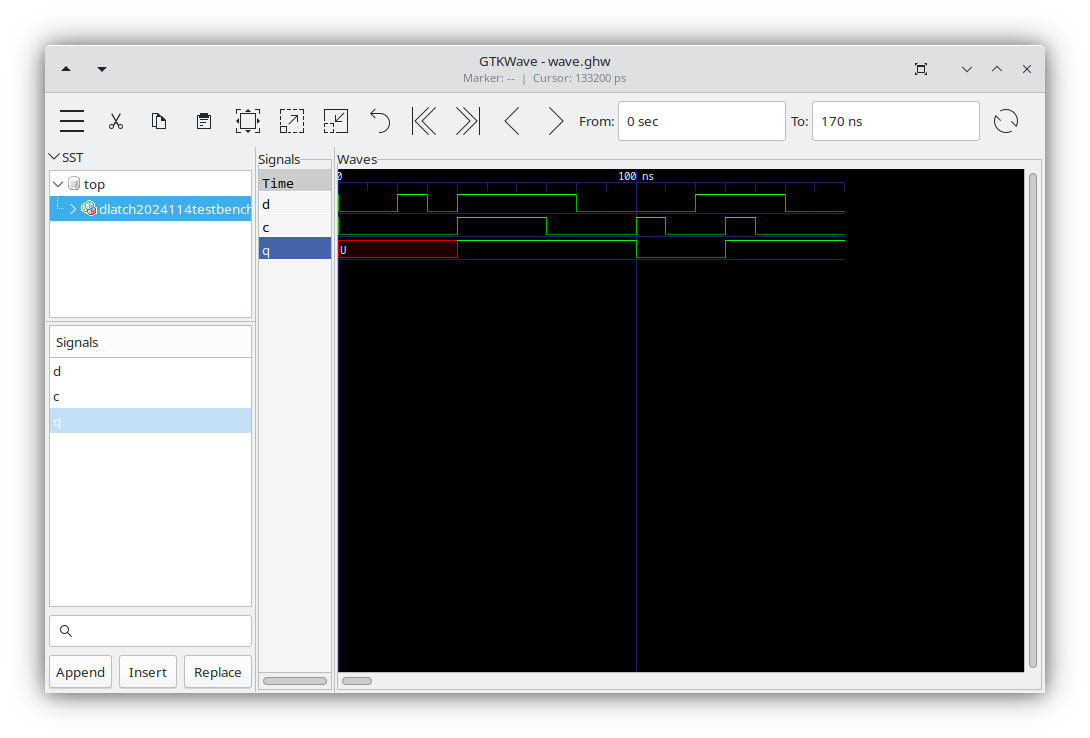

Es tut, und das ist ein wenig absurd, ich erkläre den Fehler

Dies Mal zeigt das ganze D-Latch das richtige Verhalten

Die Setzzeit spielt in dem Fall keine Rolle, das ist von dem VHDL - FPGA - Simulieren - her bedingt spielt in der Realität eine Rolle. Die Haltezeit auch nicht. in diesem Beispiel. In der Realität gilt, das Signal muss bereits stabil sein, wenn der Takt rein geht und es muss es bleiben, wenn er schon unten ist

Trotzdem nimmt es hier eine form ein - wie bei einer real existierenden Haltezeit. Doch das tut es wahrscheinlich in dieser VHDL Simulation nicht. Würde die Taktflanke von CLK genau dann runter gehen, wenn das Datensignal negative Taktflanke hätte, es wäre stabil

Aber in diesem Beispiel ist es richtig, das Datensignal bleibt, während das Taktsignal negtive Taktflanke hat.

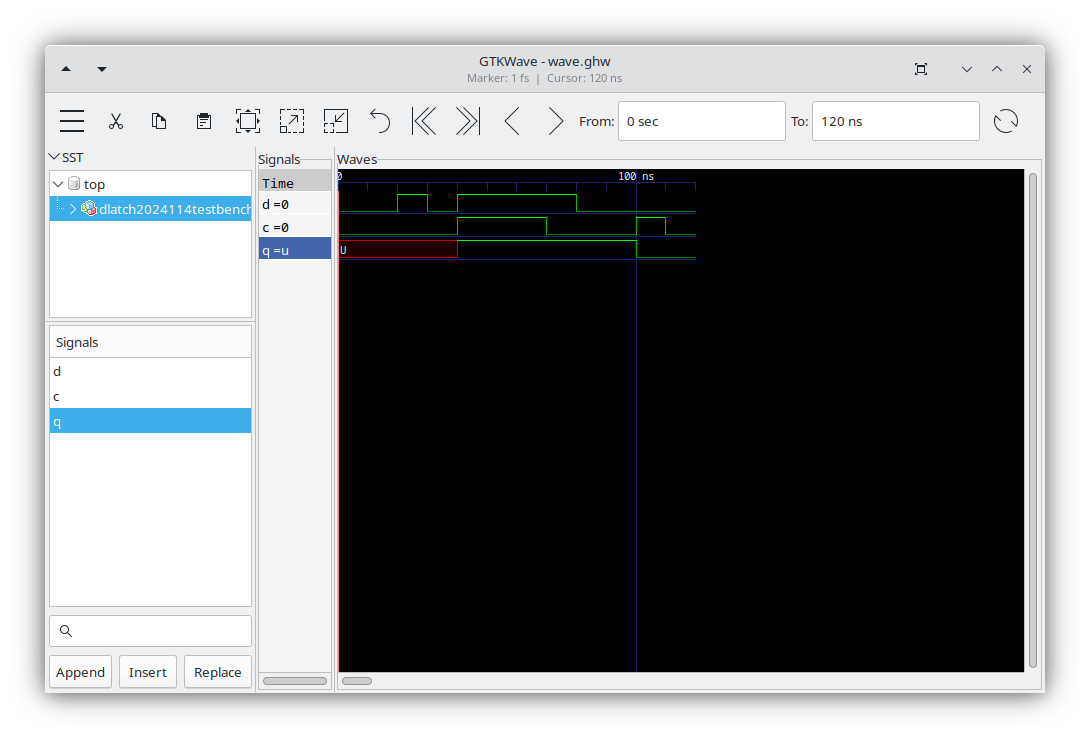

Das wäre der richtige Weg? Woher kommt das seltsame aber an sich eigentlich verständliche Ergebnis von vorher?

Interessant ist, dass wir ein RS-Latch haben und die Vorschrift lautet:

Q <= R NOR Q' Q' <= S NOR Q

Gehen wir zum D-Latch über so hätte ich jetzt gemeint, letzten endes ist es durch die Umdrehung von R und S zum RS-Latch hin, ganz egal, welches NOT D und welches D ist.

Das ist es nicht und schauen wir uns das an:

Q <= R NOR Q' Q' <= S NOR Q

Ist es nicht egal, bezogen auf D. Schauen wir uns D korrekt an:

dr <= not d;

ds <= d;

muss es so heissen. Drehen wir es anders herum, wie im ersten Beispiel, verhält sich die Logik entgegen den Sinn, beider

Daher rührte der Fehler und die Sache ist nun richtig.

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20241114 is

port(

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rslatch20241114 is

begin

q <= r nor qs;

qs <= s nor q;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch20241114 is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch20241114 is

component rslatch20241114

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal clkr, clks: std_logic;

begin

rs: rslatch20241114 PORT MAP (r=>clkr, s=>clks, q=>q, qs=>qs);

clkr <= c and r;

clks <= c and s;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114 is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114 is

component clktriggeredrslatch20241114

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal ds, dr: std_logic;

begin

clkrs: clktriggeredrslatch20241114 PORT MAP (r=>dr, s=>ds, c=>c, q=>q);

dr <= not d;

ds <= d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114testbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114testbench is

component dlatch2024114

port (

q: inout std_logic;

c: in std_logic;

d: in std_logic

);

end component;

signal c, d: std_logic;

begin

dl: dlatch2024114 PORT MAP (d=>d, c=>c, q=>q);

d <= '0' after 0 ns, '1' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns;

c <= '0' after 0 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '0' after 70 ns, '1' after 100 ns, '0' after 110 ns, '0' after 120 ns;

end;

wir müssen uns merken, für den MIPS32 - später - das geht schnell, no panic

Welche schaltungen gibt es in Computersystemen I/II?

Addierer, Kodierer, Dekodierer, würde ergänzen Encode, Multiplexer, Demultiplexer, Register, Subtrahierer, ...

Wer Angst hat vor dem Befehlsdekoder.

Dem sei eines gesagt. Davor hätte ich keine Panik

Eine DNF - mit vielen Ausgängen, also ein Kodierer. Das ist nicht tragisch. Ansonsten bleiben ein paar MUX und Register

Na ja, das ist das eigentlich interessante - das ausgerechnet, die 32-Bit und der Registersatz mit 32 Bit, die Herausforderung darstellen. Sonst nichts

Aber zwei Sachen

Wohl kaum. Es ist unabhängig von der Notwendigkeit RS-Latch zu üben, Teil der Entwicklung, sie nachher vor zu stellen und keine Krakselei zu haben

Wir haben nur ein Problem. Das wollte ich damit lösen, dass ich eine Leitung hineinführte. Das ganze ist ein Schaltwerk - so zu begreifen. Die ausgänge wirken sich auf die Eingänge aus. Da diese instabil sind, wird die Schaltung es bleiben. Ich wollte das problem durch eine Interne Leitung lösen. Ich habe eine bessere Idee. Nach dem RESET sind alle Ausgänge der Register abgekoppelt, bis die Speicherglieder stabil sind.

-- es tut, und jetzt kommt der letzte elchtest

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20241114 is

port(

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rslatch20241114 is

begin

q <= r nor qs;

qs <= s nor q;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch20241114 is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch20241114 is

component rslatch20241114

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal clkr, clks: std_logic;

begin

rs: rslatch20241114 PORT MAP (r=>clkr, s=>clks, q=>q, qs=>qs);

clkr <= c and r;

clks <= c and s;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114 is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114 is

component clktriggeredrslatch20241114

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal ds, dr: std_logic;

begin

clkrs: clktriggeredrslatch20241114 PORT MAP (r=>dr, s=>ds, c=>c, q=>q);

dr <= not d;

ds <= d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114testbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114testbench is

component dlatch2024114

port (

q: inout std_logic;

c: in std_logic;

d: in std_logic

);

end component;

signal c, d: std_logic;

begin

dl: dlatch2024114 PORT MAP (d=>d, c=>c, q=>q);

d <= '0' after 0 ns, '1' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns;

c <= '0' after 0 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '0' after 70 ns, '1' after 100 ns, '0' after 110 ns, '0' after 120 ns;

end;

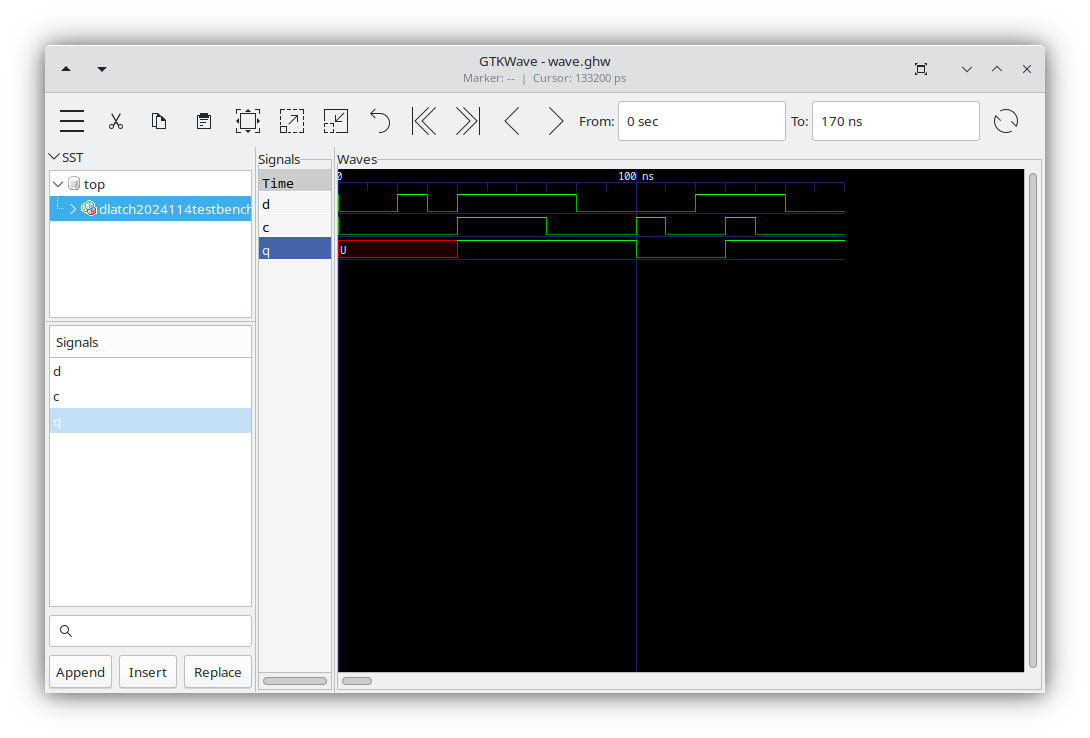

-- es scheint zu halten, was es verspricht

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20241114 is

port(

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of rslatch20241114 is

begin

q <= r nor qs;

qs <= s nor q;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch20241114 is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch20241114 is

component rslatch20241114

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal clkr, clks: std_logic;

begin

rs: rslatch20241114 PORT MAP (r=>clkr, s=>clks, q=>q, qs=>qs);

clkr <= c and r;

clks <= c and s;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114 is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114 is

component clktriggeredrslatch20241114

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic;

qs: inout std_logic

);

end component;

signal ds, dr: std_logic;

begin

clkrs: clktriggeredrslatch20241114 PORT MAP (r=>dr, s=>ds, c=>c, q=>q);

dr <= not d;

ds <= d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch2024114testbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatch2024114testbench is

component dlatch2024114

port (

q: inout std_logic;

c: in std_logic;

d: in std_logic

);

end component;

signal c, d: std_logic;

begin

dl: dlatch2024114 PORT MAP (d=>d, c=>c, q=>q);

d <= '0' after 0 ns, '1' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '0' after 150 ns;

c <= '0' after 0 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '0' after 70 ns, '1' after 100 ns, '0' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '0' after 170 ns;

end;

Das ist schön für sie - aber ein MIPS32 - ist schnell gemacht, und der sehr schnell, sehr viel besser. Es ist nicht so tragisch, eine Pipeline mit IF, ID, EX, MEM, WB ein zu führen und es ist nicht so tragisch ihn immer weiter zu erweitern, dabei hat man ihn schnell Und wer weiss, vielleicht läuft irgendwann ihr Linux auf ihrem FPGA - Linux gibt es für MIPS32.